10 Ways AI is Revolutionizing Analog Chip Design in 2025

- jenniferg17

- Jul 28, 2025

- 4 min read

Updated: Aug 7, 2025

Read Below:

AI is revolutionizing analog chip design by automating key workflows, from circuit sizing and layout migration to verification and defect detection, using advanced machine learning models like reinforcement learning, graph neural networks and diffusion models.

Innovations in analog in-memory computing, energy-efficient AI chips and time-based signal processing are redefining performance and power efficiency, while predictive AI tools tackle aging, reliability and manufacturing variability at an unprecedented scale.

At McKinsey Electronics, we’re closely tracking these breakthroughs to help clients across the Middle East, Africa and Türkiye region adopt AI-driven analog design flows, access cost-effective advanced components and confidently build the next generation of intelligent hardware.

Artificial Intelligence (AI) is profoundly transforming analog chip design, introducing unprecedented levels of efficiency, precision and innovation. In 2025, AI's integration into this field is evident through several highly technical advancements that leverage cutting-edge machine learning models, optimization frameworks and advanced EDA toolchains. Here are 10 ways AI is shaping the future of analog IC design, in depth:

1. AI-Driven Design Automation

Synopsys' AgentEngineer is an AI-driven tool designed to assist engineers in managing the complexities of modern chip design, particularly for AI server systems involving thousands of interconnected chips. While Synopsys has not publicly disclosed specific part numbers or model architectures, AgentEngineer is embedded into the Synopsys EDA stack, likely leveraging reinforcement learning (RL) agents trained on millions of historical design runs. These agents can optimize schematic design testing, analog simulation scheduling and testbench generation. By abstracting repetitive manual tasks, AgentEngineer enables high-throughput design cycles without scaling engineering headcount.

2. Enhanced Analog Design Migration

Synopsys offers analog design migration tools that leverage AI, similar in spirit to DSO.ai, to help port analog IPs to new nodes with fewer manual iterations. The tool uses supervised learning and transfer learning to infer how transistor-level designs should be restructured across PDKs (Process Design Kits). ASO.ai considers mismatch, IR drop, layout-dependent effects (LDEs) and parasitic extraction models during its migration strategy. It tightly integrates with Synopsys Custom Compiler and PrimeSim SPICE to maintain electrical equivalence in migrated layouts.

3. AI-Optimized Circuit Sizing

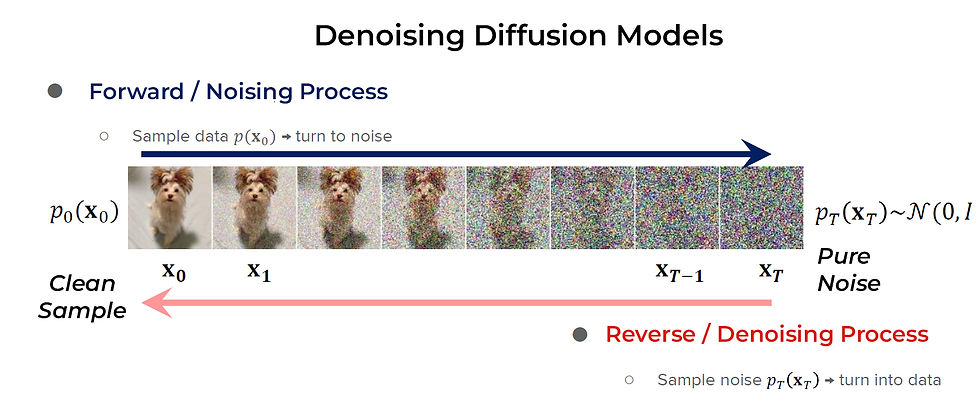

Circuit sizing is traditionally handled through iterative corner simulations and designer heuristics. In 2025, DDPMs (Denoising Diffusion Probabilistic Models) show promise for automating analog circuit sizing, although this is still mainly in the research stage and not yet widely deployed in commercial EDA tools. These models generate analog circuit parameters (e.g., W/L ratios, bias currents) by denoising a Gaussian prior conditioned on performance targets (like gain, bandwidth and power). Trained on SPICE simulation data, DDPMs drastically reduce exploration time in large parameter spaces. They are integrated into flow pipelines via PyTorch-based toolkits and co-simulated using Spectre or HSPICE.

4. Predictive Maintenance and Aging Analysis

AI is now enabling circuit-level aging predictions using time-series models like LSTM (Long Short-Term Memory) networks and physics-informed neural networks (PINNs). These systems model Negative Bias Temperature Instability (NBTI), Hot Carrier Injection (HCI), and Electromigration (EM) over mission profiles. Trained on historical failure analysis (FA) data, they predict drift in threshold voltages and current degradation. This foresight allows foundries and OEMs to apply dynamic guardbanding or circuit reconfiguration to extend chip lifetimes.

5. AI-Enhanced Design Verification

Siemens' Solido Design Environment applies supervised learning, kernel regression, and Gaussian process modeling to accelerate analog verification. Solido ML Characterization automatically learns the parameter space and corners of interest, dramatically reducing the number of required simulations. Using hyperdimensional approximation methods, it predicts circuit performance across process-voltage-temperature (PVT) corners, saving weeks of SPICE time. Solido also supports variance-aware Monte Carlo (VAMC) analysis with intelligent sampling techniques.

6. Analog In-Memory Computing Architectures

Analog IMC is reshaping edge-AI accelerators. Frameworks like LIMCA utilize large language models (LLMs) and transformers to generate SPICE-level netlists of analog matrix-vector multipliers. LIMCA parses high-level DNN structures (e.g., ResNet, Transformer blocks) and maps them into crossbar topologies using memristors or RRAM devices. AI guides trade-offs between non-linearity correction circuits and peripheral analog DAC/ADC bandwidth. These architectures are benchmarked using IMC-aware energy-delay product (EDP) metrics.

7. AI-Driven Defect Detection

TSMC, Intel and Samsung now employ AI models for sub-nanometer wafer inspection. AI-driven Automatic Defect Classification (ADC) tools use convolutional neural networks (CNNs) trained on inline SEM imagery and e-beam pattern recognition to detect killer defects with pixel-level precision. These systems run on NVIDIA DGX clusters and integrate with yield learning platforms (like PDF Solutions’ Exensio). The result: faster ramp-to-yield, reduction in false positives and real-time defect source analysis.

8. Energy-Efficient Analog AI Chips

IBM Research’s analog AI chips use phase-change memory (PCM) and hybrid-CMOS front-ends to process vector-matrix operations in-memory. The chip fabric integrates analog accumulators and resistive weight cells in a tiled mesh architecture. Training-aware calibration algorithms handle non-idealities (e.g., write drift, variability) using AI. The chip achieves over 12 TOPS/W and supports token-by-token LLM inference, outperforming GPUs for low-latency, low-power AI workloads. It's co-designed using ONNX-compatible training loops and custom analog macros.

9. AI in Time-Based Signal Processing

AI is optimizing key building blocks in time-based analog signal processing (e.g., phase-domain filters, time amplifiers). Deep RL models are applied to optimize Voltage-Controlled Oscillator (VCO) linearity and jitter performance under supply-noise injection. Generative AI also aids in designing time-to-digital converters (TDCs) with improved INL/DNL specs. These models are trained on time-domain transient simulations and validated using Cadence’s SpectreRF.

10. AI-Driven Topology Generation

Topology synthesis is undergoing a revolution with tools like AnalogGenie and LaMAGIC. These models treat circuit generation as a graph completion task, using graph neural networks (GNNs) to output netlists from high-level specs (e.g., gain, bandwidth, CMFB requirements). The models are trained on open analog design corpora (like the OAC dataset) and include self-attention mechanisms to understand node hierarchy and feedback paths. Generated topologies are instantly SPICE-valid and integrate with layout generators for push-button PDK compatibility.

AI is transforming analog design by completely changing how the work gets done, not just supporting it. From topology generation to reliability modeling, every stage of the design pipeline now benefits from predictive intelligence, deep learning inference and automation, opening a new era of analog design in 2025 and beyond. At McKinsey Electronics, we see firsthand how AI is reshaping analog chip design, and we're committed to supporting that transformation every step of the way. As a trusted semiconductor distributor in the Middle East, Africa and Türkiye region, we provide the components and local engineering support that next-gen analog designers rely on. Whether you're integrating AI-enhanced verification flows, experimenting with time-domain architectures or sourcing for energy-efficient analog AI chips, our team helps you identify cost-effective parts and equivalents that align with your innovation goals.